Bar-Ilan University 83-612: Digital VLSI Design

This is Lecture 5 of the Digital VLSI Design course at Bar-Ilan University. In this course, I cover the basics of Chip Implementation, from designing the logic (RTL) to providing a layout ready for fabrication (GDS).

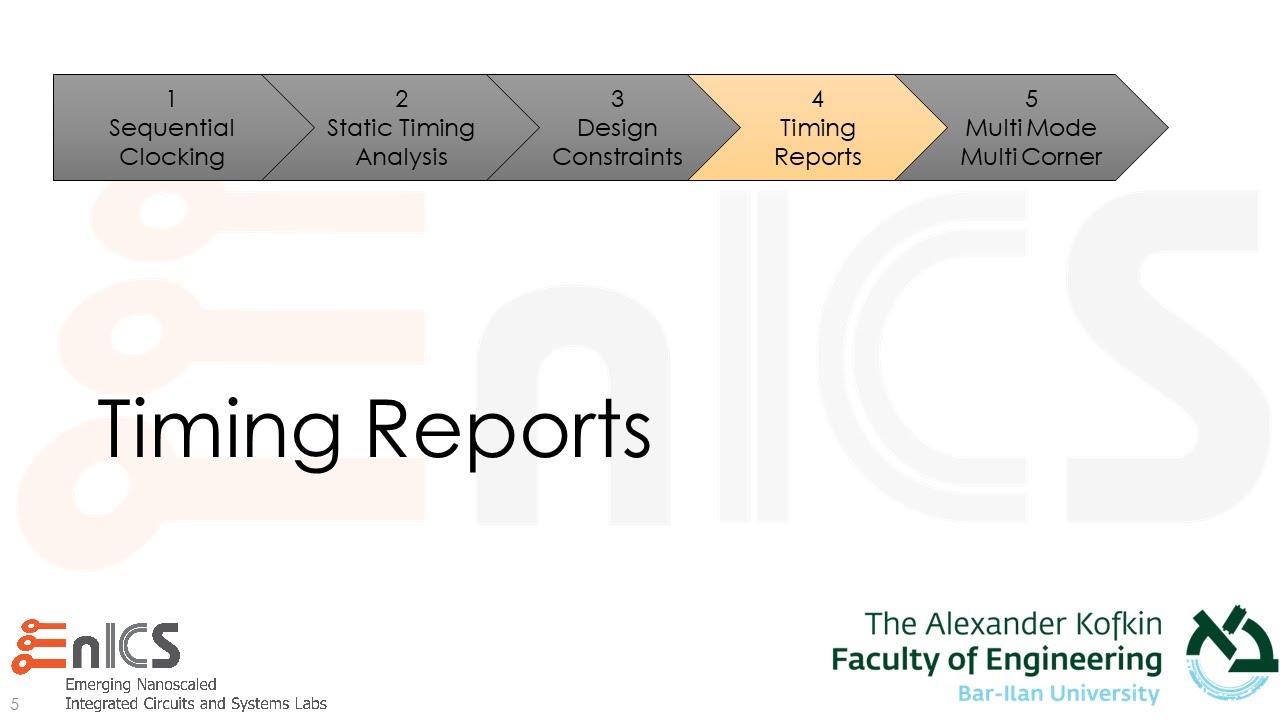

Lecture 5 covers the basics of static timing analysis (STA), used for optimization and for constraint checking. Timing is covered from both an algorithmic and a practical level, including examples of implementations in the Cadence work flow.

Lecture 5g demonstrates what a timing report looks like and how to read it.

Lecture slides can be found on the EnICS Labs web site at:

[ Ссылка ]

All rights reserved:

Prof. Adam Teman

Emerging nanoscaled Integrated Circuits and Systems (EnICS) Labs

Faculty of Engineering, Bar-Ilan University

DVD - Lecture 5g: Timing Reports

Теги

Chip DesignBar-Ilan UniversityVLSIBackendVerilogSynthesisPlace and RouteCadenceLayoutAlgorithms83612Adam TemanAdi TemanEnICS LabsSemiconductorsStatic Timing AnalysisSTAreport_timingTiming ReportsSDCSynopsys Design ConstraintsSynchronousSetupHoldMax DelayMin DelaySlackDAGNode Based Timing AnalysisOptimizationMMMCMulti-Mode Multi-CornerMulti-Corner Multi-ModeStylusCommon UIRISC-V